Ensuring the robustness and accuracy of modern integrated circuits (ICs) is paramount, and rigorous testing is a critical step in this process. Thorough testing not only guarantees the quality of chips but also provides significant cost savings and time efficiency by identifying and rectifying inefficiencies early in the design cycle. However, the complexity of modern designs can sometimes lead to less comprehensive testing than desired, often because the design itself is not inherently testable.

This is where Cadence’s Test Solution, featuring seamless integration between Genus Synthesis Solution and Modus Test Solution, becomes invaluable. It serves as a cornerstone of the digital platform, specifically designed to make designs testable from the ground up. The tight integration with one-pass synthesis workflows ensures predictable and reliable outcomes in your design process. The Cadence Test Solution is more than just a point tool; it provides a complete and cohesive flow for ensuring testability:

- It expertly utilizes the Genus infrastructure to efficiently insert, connect, and verify Design for Testability (DFT) logic.

- Capitalizing on physical synthesis and power-aware methodologies for optimized performance and efficiency.

- Offers a dedicated Test Point insertion flow, strategically augmenting test coverage and fault detection.

- Provides a robust interface to the Modus DFT Software Solution, facilitating advanced Automatic Test Pattern Generation (ATPG) and diagnostic capabilities.

Cadence Test Solution integrates Genus and Modus for comprehensive DFT

Cadence Test Solution integrates Genus and Modus for comprehensive DFT

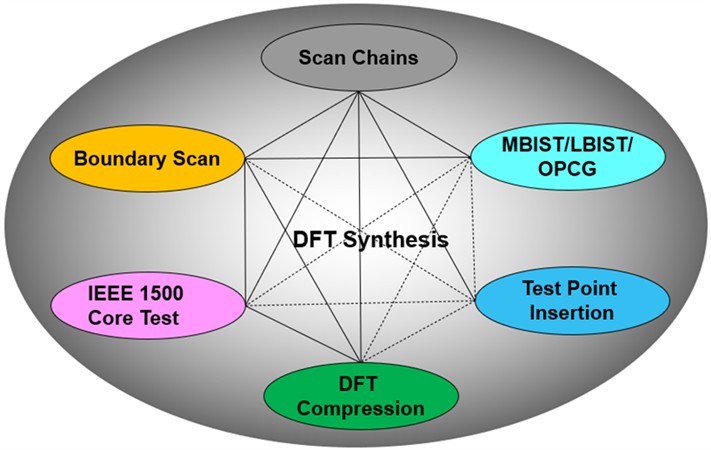

Cadence Genus Synthesis Solution plays a pivotal role in synthesizing DFT-integrated netlists. It achieves this by employing a series of critical steps, including setting and executing DFT rule checks, resolving any DFT violations, enhancing the overall testability of the design, and meticulously configuring and connecting scan chains. The DFT capabilities embedded within Genus Synthesis are extensive and cover a wide range of testability features:

- Comprehensive checking of DFT rules to ensure robust scan chain creation and integrity.

- Creation of abstract scan chain models, simplifying complex test structures for easier management.

- Strategic insertion of shadow logic around areas of the design that are inherently difficult to test, improving fault coverage.

- In-depth analysis of logic for testability bottlenecks and intelligent insertion of test points to boost fault detection.

- Flexible configuration of DFT constraints and automated connection of scan chains, streamlining the DFT implementation process.

- Insertion of Boundary Scan logic, enabling board-level testing and system integration validation.

- Implementation of PMBIST (Processor Memory Built-In Self-Test) logic for efficient memory testing.

- Integration of advanced test Compression logic, reducing test data volume and test application time.

- Incorporation of OPCG (Observation Point Control Group), 1500 Core Wrapper, and LBIST (Logic Built-In Self-Test) methodologies to address diverse test requirements.

- Generation of essential output files including scan DEF (Design Exchange Format) and ATPG interface files, ensuring seamless integration with downstream tools.

These test synthesis features within Genus operate with intricate interactions and interdependencies, highlighting the sophistication and power of the Cadence Test Solution.

To delve deeper into enhancing your design testability by effectively configuring and connecting scan chains, and leveraging advanced testability features such as Boundary Scan, PMBIST, Compression, OPCG, and IEEE 1500 Wrapper using Genus Synthesis Solution, Cadence offers an invaluable online course: Test Synthesis with Genus Stylus Common UI Training v23.1.

This Test Synthesis with Genus Stylus Common UI Training v23.1 course provides hands-on knowledge and practical skills, enabling you to:

- Effectively constrain your design specifically for Design for Testability (DFT) requirements.

- Proficiently run DFT rule checkers to identify and rectify any violations, ensuring DFT compliance.

- Synthesize your design and seamlessly map it for scan insertion, preparing it for test.

- Configure DFT constraints and gain a preview of scan chains, allowing for early verification and optimization.

- Implement robust scan chain connections, forming the backbone of your test strategy.

- Execute hierarchical scan insertion for complex designs, managing testability at different levels of hierarchy.

- Troubleshoot and resolve common scan-related issues, ensuring a smooth DFT implementation process.

- Utilize advanced testability features including Boundary Scan, PMBIST, Compression, OPCG, and IEEE 1500 wrapper, expanding your test capabilities.

Enroll in this comprehensive Online Training by following these simple steps:

- Navigate to “Learning” from the main menu and select “Online Courses”.

- Use the search bar to find “ATPG Flow with Modus DFT Software Solution”.

- Select the relevant course and click “Enroll” to begin your journey towards mastering test synthesis.

Upon successful completion of the online training, Cadence Training Services offers a prestigious Digital Badge to recognize and showcase your expertise gained through the training. This Digital Badge can be readily added to your email signature or professional networking platforms like LinkedIn and Facebook, effectively highlighting your proficiency in Cadence tools and methodologies.