Testing digital integrated circuit (IC) designs is paramount in modern semiconductor development. It’s not merely about ticking a box; rigorous testing directly impacts cost efficiency, development timelines, and the overall performance of the final product by identifying and rectifying inefficiencies early in the design cycle. Ensuring the testability of your design is the first critical step in this process. A design that is not inherently testable can lead to significant roadblocks in achieving comprehensive verification, regardless of the sophistication of testing methodologies applied later.

The Cadence Test Solution, deeply integrated with the Genus Synthesis Solution and Modus Test Solution, provides a powerful and cohesive platform to address design testability head-on. This integration, especially with Cadence’s one-pass synthesis flow, ensures predictable outcomes and a streamlined approach to Design for Testability (DFT). The Cadence Test Solution offers a comprehensive suite of features, including:

- Utilizing Genus infrastructure for seamless insertion, connection, and verification of DFT logic.

- Leveraging physical synthesis and power-aware methodologies for optimized test implementation.

- Incorporating Test Point insertion flows to maximize fault coverage and enhance test effectiveness.

- Interfacing seamlessly with the Modus DFT Software Solution for advanced Automatic Test Pattern Generation (ATPG) and diagnostic capabilities.

The Cadence Test Solution is engineered as a complete and integrated flow, not just a collection of isolated point tools, providing a holistic approach to DFT.

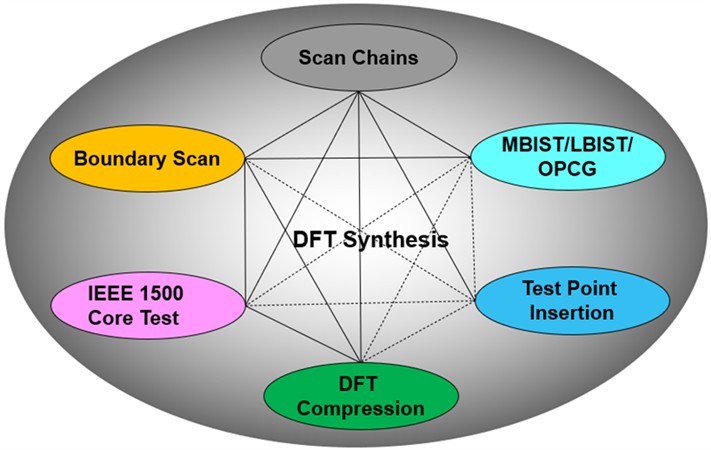

Cadence Genus Synthesis Solution plays a pivotal role in synthesizing DFT-ready netlists. This involves a series of critical steps, starting with DFT rule checking and violation resolution, progressing to design testability enhancement, and culminating in the configuration and connection of scan chains. Key DFT features embedded within Genus Synthesis include:

- DFT Rule Checking: Ensuring adherence to essential DFT guidelines during scan chain creation, preventing downstream issues.

- Scan Chain Abstraction Models: Creating simplified models of scan chains for efficient handling in synthesis and downstream DFT processes.

- Shadow Logic Insertion: Strategically inserting shadow logic around inherently untestable logic blocks to improve overall test coverage.

- Testability Analysis and Test Point Insertion: Analyzing the design’s logic to pinpoint areas of low testability and automatically inserting test points to boost fault detection.

- DFT Constraint Configuration and Scan Chain Connection: Providing robust mechanisms for configuring DFT constraints and automatically connecting scan chains according to specified architectures.

- Boundary Scan Insertion: Implementing boundary scan logic (IEEE 1149.1 standard) for board-level testing and system integration verification.

- PMBIST Logic Insertion: Incorporating Processor-based Memory Built-In Self-Test (PMBIST) logic for efficient and autonomous testing of embedded memories.

- Test Compression Logic Insertion: Integrating advanced test compression techniques to reduce test data volume and test application time, critical for complex designs.

- OPCG and IEEE 1500 Core Wrapper & LBIST Insertion: Supporting On-Chip Programmable Clock Generator (OPCG) insertion for flexible clocking schemes in test mode, IEEE 1500 core wrapper for core-based DFT methodologies, and Logic Built-In Self-Test (LBIST) for logic testing.

- Scan DEF and ATPG Interface File Output: Generating essential output files like Scan Design Exchange Format (DEF) and ATPG interface files, facilitating seamless transitions to downstream DFT tools like Modus.

Cadence Genus Synthesis Solution integrating DFT features for scan chain creation and testability enhancement

Cadence Genus Synthesis Solution integrating DFT features for scan chain creation and testability enhancement

These comprehensive test synthesis features within Genus are intricately designed to work synergistically, addressing the complex interdependencies inherent in modern DFT methodologies.

To gain in-depth knowledge on leveraging the Cadence Genus Synthesis Solution for enhancing design testability through scan chain configuration and advanced testability feature integration (such as Boundary Scan, PMBIST, Compression, OPCG, and IEEE 1500 Wrapper), consider enrolling in the online course: Test Synthesis with Genus Stylus Common UI Training v23.1.

This Test Synthesis with Genus Stylus Common UI Training v23.1 course is structured to equip you with practical skills in:

- Constraining designs specifically for Design for Testability (DFT) requirements.

- Executing DFT rule checks and efficiently resolving identified violations.

- Synthesizing designs and effectively mapping them for scan chain implementation.

- Setting up comprehensive DFT configuration constraints and previewing scan chain architectures.

- Connecting scan chains optimally for test coverage and efficiency.

- Implementing hierarchical scan insertion methodologies for complex System-on-Chip (SoC) designs.

- Troubleshooting and resolving common scan chain related issues.

- Implementing and utilizing advanced testability features including Boundary Scan, PMBIST, Compression, OPCG, and IEEE 1500 wrapper techniques.

To register for this valuable Online Training, follow these straightforward steps:

- Navigate to “Learning” in the menu and select “Online Courses”.

- Utilize the search bar to find “ATPG Flow with Modus DFT Software Solution”.

- Choose the course from the search results and click “Enroll”.

Upon successful completion of this online training, Cadence Training Services offers a prestigious Digital Badge to validate and showcase your expertise. This Digital Badge can be readily integrated into your email signature or professional social media platforms like LinkedIn and Facebook, effectively highlighting your proficiency in Cadence DFT methodologies.